项目概述

White Rabbit Event Node(White Rabbit 节点终端 简称WREN )项目的主要目标是开发一种通用的事件处理解决方案,能够利用 White Rabbit 网络提供的亚纳秒级同步精度,在分布式系统中精确地产生或接收触发信号。

核心功能

高精度定时:基于 White Rabbit 协议,实现亚纳秒级的时钟同步。

事件触发:支持在预定义的精确时间点产生物理触发脉冲(TTL信号)。

事件时间戳:能够对输入的外部触发信号进行精确的时间戳记录。

灵活配置:通常采用 FPGA 架构,允许根据具体的工业或科学实验需求定制逻辑。

硬件版本

目前共有以3种接口版本(所有板都基于 Xilinx/AMD Zynq Ultrascale+ System-on-Chip (SoC) 技术):

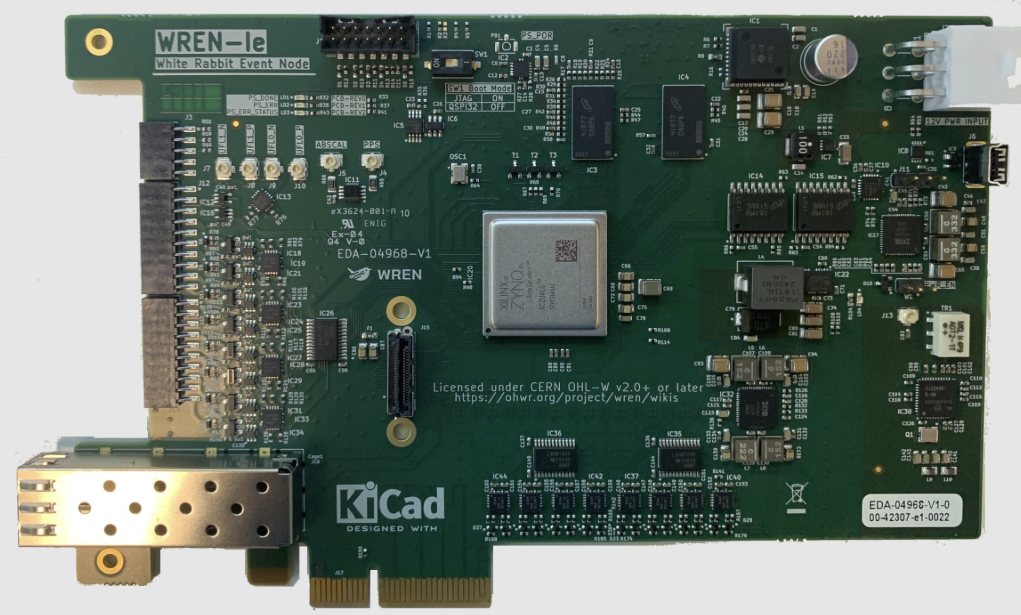

WREN Ie:PCIe 接口

ID

类别 (Category)

描述 (Description)

1

接口

PCIe Gen2 x 4

2

供电

P12V_PCIe

3

FPGA 芯片

Xilinx Zynq UltraScale+ XCZU4CG-1SFVC784E

4

DDR4 内存

2x 1GB

5

闪存 (Flash)

128MB QSPI32

6

启动

支持 JTAG 或 QSPI 启动;

板载 PS_DONE、PS_ERR、PS_ERR_STATUS 状态指示灯

7

White Rabbit (WR)

1G WR 电路,用于时钟同步和数据恢复

SFP 收发器连接至 FPGA PL端的 GTH 收发器

EEPROM 中存有唯一的 MAC 地址识别码

板载 U.FL 连接器,用于 WR CLK MAIN(主时钟)、PPS(秒脉冲)及 ABSCAL(绝对校准时钟)输出

8

PS 时钟

50 MHz

9

PL GTH 收发器

1路 WR-SFP 接口

2路 RF 束团时钟(RF BUNCH CLK1/2,SansDAC 方案),在 FPGA 内部回环至一对 HP(高性能)引脚

10

面板 IO接口

2路输入,4路通用 IO

输入端:具备过压/欠压保护;每个 IO 可独立启用终端电阻

输出端:支持 50Ω 负载下的 3V 驱动电平;每个 IO 可独立启用输出

所有前板 IO 均为单端信号,连接至 FPGA 的 HP Bank

11

面板 其他

每个 IO 对应一个 RGB LED 指示灯

1路 SFP 状态 RGB LED

2路板卡状态 RGB LED

前面板 PCB 硬件版本识别功能

12

配线架 输出

采用 Samtec 微型同轴连接器连接至配线架 PCB

32路 TTL 3V 输出,支持 50Ω 负载(仅限输出!)

13

配线架 其他

每个 IO 对应一个 RGB LED 指示灯

1路配线架状态 RGB LED

配线架 PCB 硬件版本识别功能

14

其他

JTAG 连接器

第二路 SFP 笼子(可选,用于未来的 WR 冗余或不同链路)

PS-UART 调试口:micro-USB 接口

支持 FPGA 读取 PCB 版本号

15

设计工具

KiCad v9

16

授权协议

CERN OHL-W v2.0+

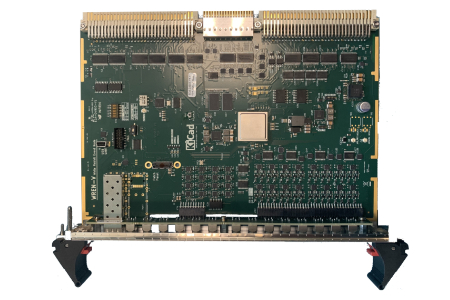

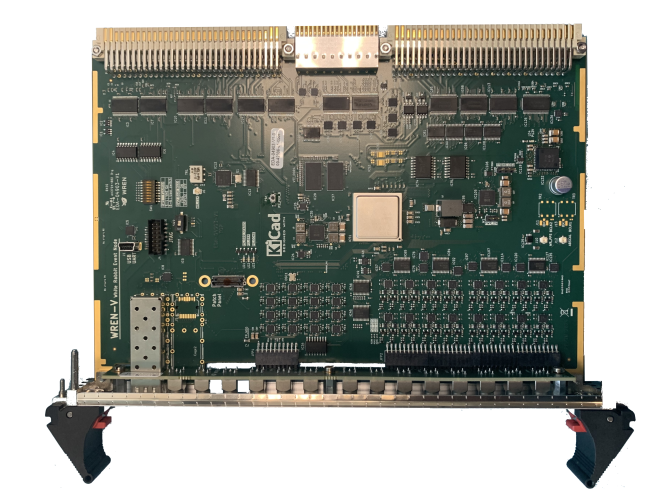

WREN V:VME接口

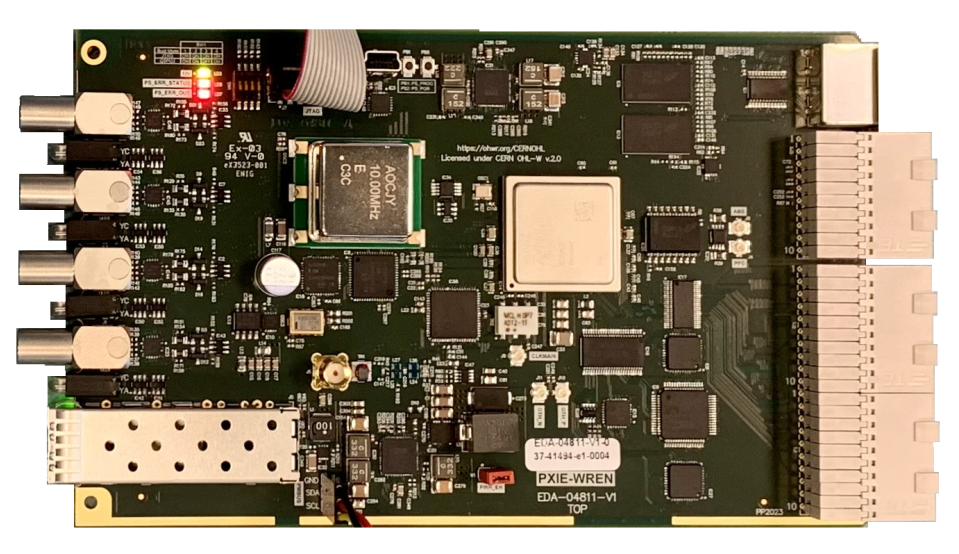

WREN-XIe:PXIe接口(未发布设计文件)

Licences

CERN Open Hardware Licence v1.2